1) 基于Zynq Soc 的(de)開源平台:

采用Zynq Soc芯片,內(nèi)部封裝了雙核Arm CPU以及Xilinx FPGA,雙方通過AXI總線互聯,由于內(nèi)部的(de)高(gāo)集成度以及較高(gāo)的(de)總線帶寬,

CPU能夠将部分計算任務分配給FPGA,結合FPGA的(de)高(gāo)速并行(xíng)計算能力,能夠為(wèi)用戶需求提供足夠靈活的(de)報文處理(lǐ)能力。

2) 實現基本的(de)數據平面交換功能:

FAST開源項目具有(yǒu)一(yī)個可(kě)擴展的(de)框架。湖南新實基于FAST開源項目框架首先實現了一(yī)些基本的(de)網絡交換功能,例如(rú)L2 交換,

L3 路由和(hé)openflow 交換等。這樣用戶可(kě)以關注和(hé)使用開源項目代碼搭建自(zì)己的(de)網絡環境。

3) 支持軟件定義時間敏感網絡SD-TSN:

SD-TSN 網絡既具備軟件定義網絡的(de)組網靈活性、協議無關轉發的(de)高(gāo)适應性、轉發控制分離(lí)的(de)高(gāo)效性與可(kě)控性,同時又具有(yǒu)低(dī)延時、低(dī)抖動的(de)時間敏感特性。

通過軟件流表與隊列映射的(de)靈活定義,極大放寬了全網流規劃調度的(de)難度,增強了TSN網絡的(de)适用範圍和(hé)行(xíng)業兼容性。

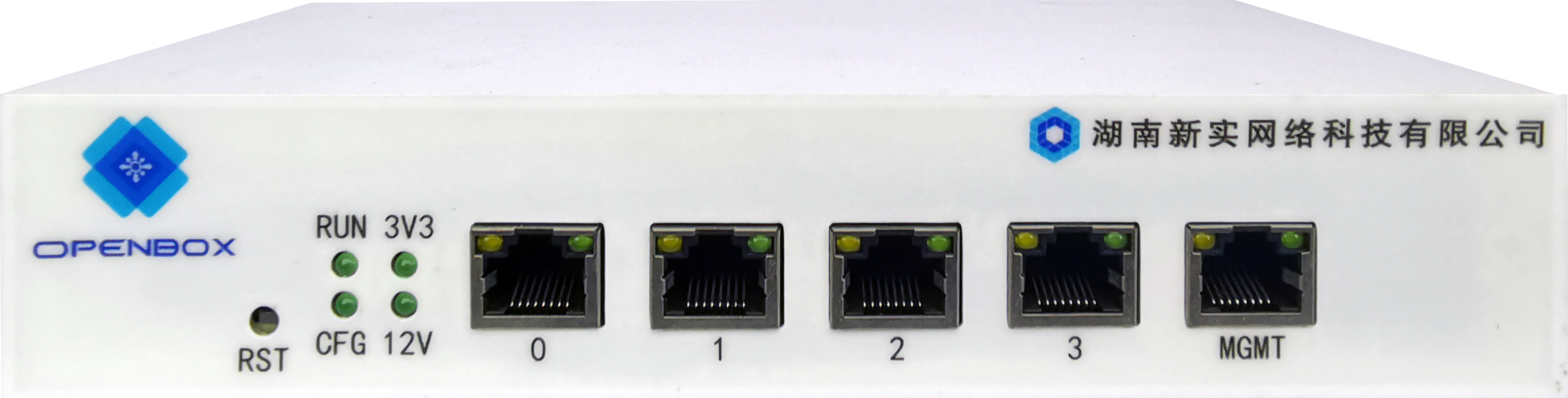

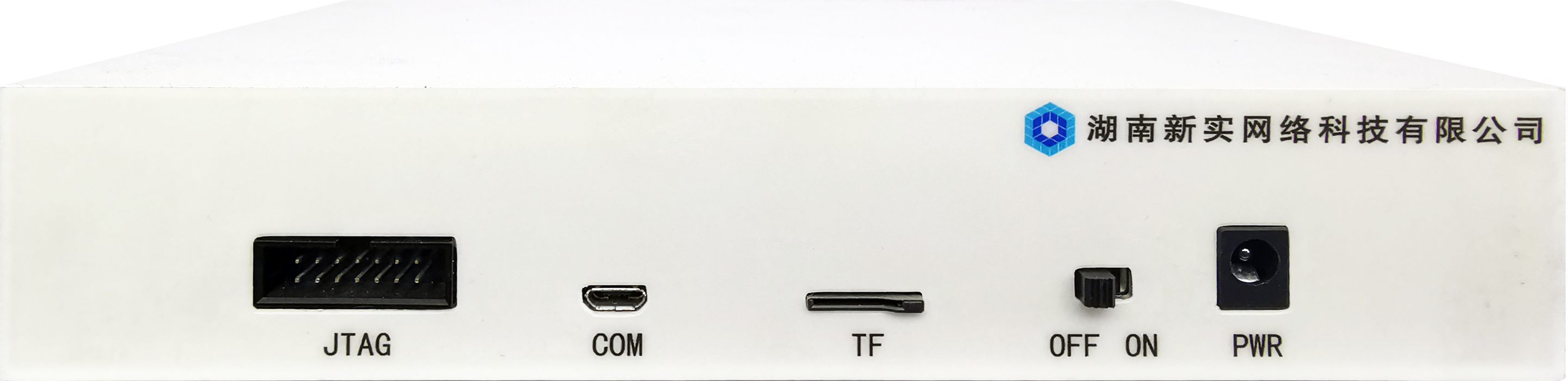

OpenBox-S4設備支持部署成TSN交換機(jī)節點和(hé)實時TSN端網卡節點兩種設備角色。OpenBox-S4設備支持TSN系統與硬件時鍾同步/校正、Qbv周期調度API接口、CB功能流管理(lǐ)API接口、QCI隊列管理(lǐ)API接口等功能。

4) 支持用戶基于開源平台實現自(zì)己的(de)創新工作:

用戶可(kě)以在開源平台基礎上實現自(zì)己的(de)創新工作,而不用重新設計一(yī)個完整的(de)數據平面。

例如(rú)用戶可(kě)以在硬件中增加定制模塊來支持新的(de)協議處理(lǐ),或是在硬件邏輯中中設置一(yī)個“鈎子(zǐ)”,将指定流量定向到CPU,通過編寫軟件代碼實對特定流量施加特定處理(lǐ)。